在先進的CMOS製程裡,LOD (Length of Diffusion) Effect將會是影響類比電路的一個重要參數。

剛好最近讀了一些有關LOD Effect的文章,發現LOD Effect的資訊幾乎都是英文的,故想用正體中文把這LOD Effect做個簡單的介紹,讓初次碰到LOD Effect的Designer可以快速進入狀況。

我把文章分成上、下兩篇,上集先簡單介紹LOD Effect,接著是如何模擬LOD Effect對MOS的影響。

而下集介紹如何避免LOD Effect對電路的影響。

什麼是LOD Effect?

LOD是Length of Diffusion 的縮寫,直接翻譯就是擴散區長度所造成的影響。從025um以下的製程,元件與元件間是利用較先進的STI(Shallow Trench Isolation)的方法來做隔絕。由於STI的作法,會在substrate上挖出一個溝槽,再填入二氧化矽當絕緣層。這個在substrate挖出溝槽的動作會產生應力的問題,由於FOX(Field Oxide)到Poly Gate的距離不同,應力對MOS的影響也不同。所以當擁有相同的Gate Length和Gate Width的兩個MOS,因為擴散區長度不同造成其電流不同。

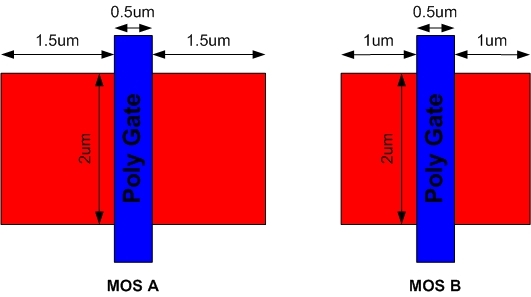

如下圖一,兩個MOS (A和B)其Gate Length與Gate Width皆為0.5um和2um,但由於擴散區分別為1um和1.5um,所以其電流大小並不同。

圖一:

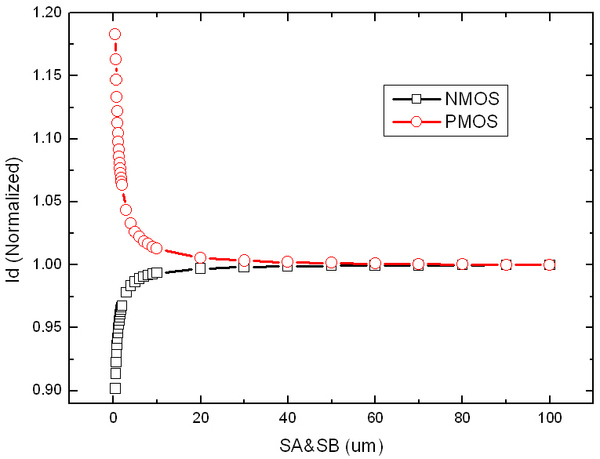

LOD Effect對PMOS和NMOS的影響正好相反。當PMOS的電流隨SA(SB)變小而變大,NMOS的電流影響則是SA(SB)越小電流越小。

如何模擬LOD Effect?

我一般都是用HSPICE做電路模擬,所以這裡介紹用HSPICE來模擬LOD Effect對電路的影響。傳統的BSIM3 SPICE Model並沒有把LOD Effect的效應估算進去,而BSIM4的Spice Model開始支援LOD Effect,所以要模擬LOD Effect必須使用BSIM4的Model。目前晶圓廠的先進製程都已提供支援BSIM4的Model給客戶使用了。

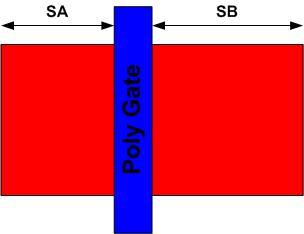

LOD Effect最重要的參數就是擴散區長度。由於Drain和Source的擴散區長度不一定相同,所以一顆MOS有SA和SB兩個參數描述LOD Effect所造成的影響,如下圖二所示。

圖二:

所以在SPICE Netlist裡,再加上SA, SB兩個參數即可,如下面M1這個MOS,在Model Name之後加入SA、SB參數。

===================================================

M1 VD VG VS VB NMOS L=0.5U W=2U SA=1U SB=1.5U

===================================================

由於SA、SB長度是由Layout決定的,所以在做Pre-Sim時,可以預先估計SA、SB的大小代入SPICE Netlist中做模擬。當Layout完成後,可由Calibre、Assura、Star-RCXT等寄生參數萃取軟體(Layout Parasitics Extraction )把SA、SB抓出來,再利用HSPICE做Post-Layout Simulation。

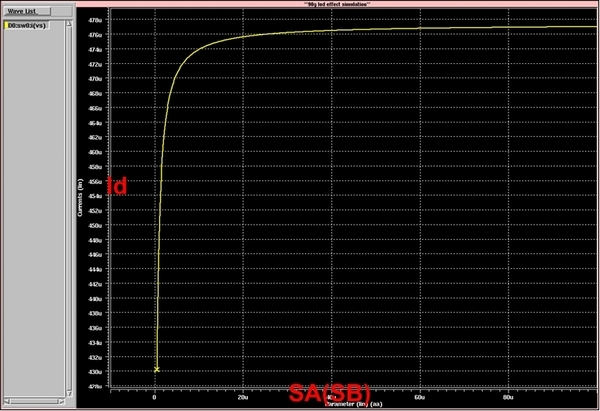

圖三是我用HSPICE做單一顆NMOS電流的模擬,X軸為SA(SB)的大小,Y軸為電流大小。我們可以看到,當SA(SB)較小的時候,NMOS的電流比較小,當SA(SB)越來越大時,電流也變大,當SA(SB)大到一定程度時,電流有飽和的趨勢。

圖三:

圖四一是對PMOS、NMOS用HSPICE做LOD Effect的模擬,X軸為SA(SB)的大小,從0.5um到100um,Y軸為電流大小,此電流以SA=SB=100um時的電流標準化後的結果。從圖四可以證明第一段所說明的結果,LOD Effect對PMOS和NMOS的影響正好相反。

圖四:

前面已經簡單介紹什麼是LOD Effect,並介紹如何在HSPICE裡把LOD Effect考慮進去,再下一篇文章將介紹如何利用Layout上的技巧來避免LOD Effect對電路的影響。

延伸閱讀1:Introduction to LOD Effect (下) by BuBuChen

參考文獻(References):

[1] Y. M. Sheu, et al., "Impact of STI Mechanical Stress in Highly Scaled MOSFETs," in Proc. IEEE International Symposium on VLSI Technology, Systems and Applications, 2003, pp. 76-79.

[2]P. G. Drennan, et al., "Implications of Proximity Effects for Analog Design," in Proc. IEEE Custom Integrated Circuits Conference, 2006, pp. 169-176.

留言列表

留言列表