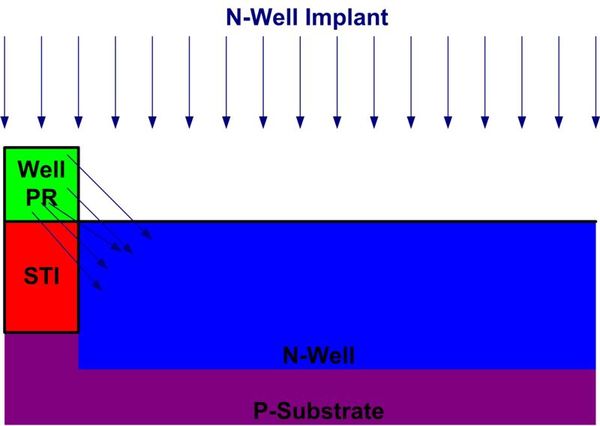

在Introduction to LOD Effect (上)一文中,已經簡單的介紹LOD (Length of Diffusion) Effect,接著來談談如何降低LOD Effect對電路的影響。LOD Effect有兩個重要參數SA、SB,由前文得知我們可以預先估計SA、SB的長度代入模擬中,這樣就可以精確的把LOD Effect考慮進去。不過實際電路設計時,你無法很準確的估計每個Device的SA(SB),尤其是Analog Circuit Layout上,還需考慮許多對稱的問題。所以一般我們只預估重要設計(Critical Block)裡面的SA(SB),再利用Layout上的技巧來降低LOD Effect對電路的影響。(註一)

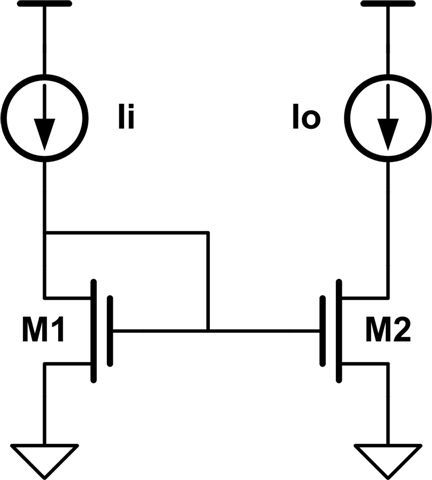

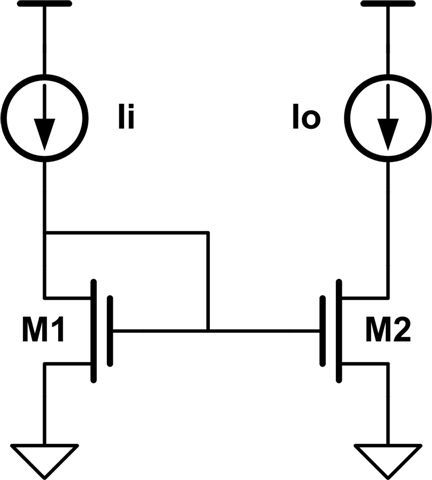

這裡用一個Current Mirror電路為例子,如圖一,Ii為輸入電流、Io為輸出電流。

圖一:

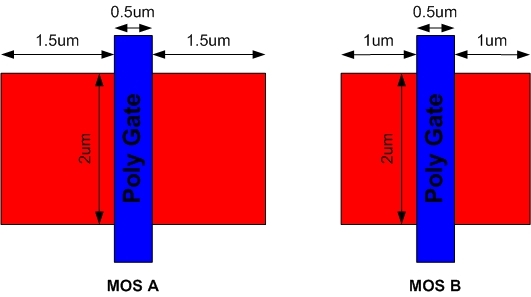

假設我們要設計Ii=Io,也就是要MOS1=MOS2。我們可以單獨把MOS1和MOS2畫出來,且SA1=SA2、SB1=SB2,如圖二。這樣LOD Effect對MOS1和MOS2的影響是相同的。

圖二:

圖二是MOS1和MOS2各只有一個Finger的狀況,假如是MOS1和MOS2為Multi Fingers呢?圖三為MOS1和MOS2各有2個Fingers的狀況,雖然MOS1和MOS2裡各自兩個Finger的SA、SB不同,但對MOS1、MOS2來說只要SA11=SA21、SB11=SB21、SA12=SA22且SB12=SB22,MOS1就是等於MOS2。所以當我們要設計Ii=Io(MOS1=MOS2)時,不論是否為Single Finger或是Multi Fingers,我們只要確定MOS1和MOS2的Layout一模一樣即可避免LOD Effect所造成的Mismatch,即使MOS1和MOS2畫在同一塊Diffussion上也是如此。

圖三:

如圖一,如果我們的設計不是Ii=Io,例如Ii=4*Io,這時我們可以單獨先把MOS1畫出來再把同樣的Layout複製4次成MOS2即可。不過為了要節省面積的關係,我們通常會把MOS1和MOS2畫在同一塊OD(difussion)上,這時Layout上就要特別注意。假設當SA(SB)大於5um時LOD Effect的影響小到可以忽略(註二), 圖四把MOS1和MOS2畫在同一塊OD上,所以我們必須把最外側(最左、最右)Fingers的OD延伸到大於5um的狀況下,這時將可以把LOD Effect影響忽略。

圖四:(MOS1有兩個fingers,MOS2有8個fingers。)

由圖四的例子可知,我們必須把重要電路(Ex: Current Mirror、Differential pair)的SA(SB)設計成>5um的狀況下,而其他不重要電路則可不遵守這樣的規則。如圖五,我們把Critical Cicuits擺在整個Diffussion中間,Non-Critical Cicuits(Ex: Switches、Dummy Devices)擺在兩旁,而Critical Cicuits最外側(最左、最右)Fingers其Gate到OD距離必須大於5um。

圖五:(Critical Circuits有6個fingers,Non-Critical Circuits有4個fingers。)

所以利用Layout上的技巧來降低LOD Effect對電路的影響最大原則就是"重要電路(Ex: Current Mirror、Differential Pair)的SA(SB)設計成>5um"(註二),其它的layout對稱問題就如一般的類比電路佈局技巧一樣(註三)。

註一:如果能預估所有元件的SA(SB)是再好不過了。

註二:不同製程下,可容忍的gate到diffusion長度皆不同,在設計電路時,要先找到這個值,在這裡是假設5um。

註三:類比電路佈局技巧可參考台北大學黃弘一教授的"混合信號積體電路設計與佈局"講義。

延伸閱讀1:Introduction to LOD Effect (上) by BuBuChen

參考文獻(References):

[1] Y. M. Sheu, et al., "Impact of STI Mechanical Stress in Highly Scaled MOSFETs," in Proc. IEEE International Symposium on VLSI Technology, Systems and Applications, 2003, pp. 76-79.

[2] P. G. Drennan, et al., "Implications of Proximity Effects for Analog Design," in Proc. IEEE Custom Integrated Circuits Conference, 2006, pp. 169-176.