到今天2013/3/15為止,共發表了IEEE Regular Journal 4篇,IEEE Brief Journal 3篇,IEEE Conference paper 11篇;申請通過了美國專利4篇,台灣專利4篇。

- Mar 15 Fri 2013 18:02

-

PUBLICATION LIST

工作後的第一篇專利通過,來更新一下。

到今天2013/3/15為止,共發表了IEEE Regular Journal 4篇,IEEE Brief Journal 3篇,IEEE Conference paper 11篇;申請通過了美國專利4篇,台灣專利4篇。

到今天2013/3/15為止,共發表了IEEE Regular Journal 4篇,IEEE Brief Journal 3篇,IEEE Conference paper 11篇;申請通過了美國專利4篇,台灣專利4篇。

- Feb 17 Tue 2009 13:16

-

2009 ISSCC Papers

每年在美國舊金山舉行的的IEEE國際固態電子電路會議(Internal Solid-State Circuit Conference,簡稱ISSCC)是IC設計界的最高盛會,世界ㄧ流的公司、學校都會在這發表重大的技術和研究成果。今年的ISSCC舉辦的時間在2月8日~12日,共五天。拿到剛出爐的2009年電子論文集,當然要趕緊看看有什麼與自己研究、工作相關的論文,此外,還要關心ㄧ下台灣今年的表現如何。

今年ISSCC共錄取了204篇論文,分別來自23個國家,台灣共有19篇文章入選,為全世界排名第三的國家,第一名是美國共有89篇入選,第二名是日本有37篇入選,第四名是韓國共有16篇論文在ISSCC 2009發表。

以下把台灣錄取的論文(第一作者皆是台灣)整理一下。(以下順序依照論文集的先後)

Paper 1

Title: A 5b 800MS/s 2mW Asynchronous Binary-Search ADC in 65nm CMOS

Affiliation: National Cheng-Kung University (成大)

Country: Taiwan

Paper 2

Title: A 600MS/s 30mW 0.13µm CMOS ADC Array Achieving Over 60dB SFDR with Adaptive

Digital Equalization

Affiliation: Industrial Technology Research

Institute (工研院); Jilin

University; University of

Illinois

Country: Taiwan; China, United States

- Nov 10 Mon 2008 23:47

-

投稿經驗--IEEE JSSC,TCAS-I,TCAS-II

- Sep 28 Sun 2008 23:36

-

Well Proximity Effect

談完LOD Effect,就不得不再談談WPE。

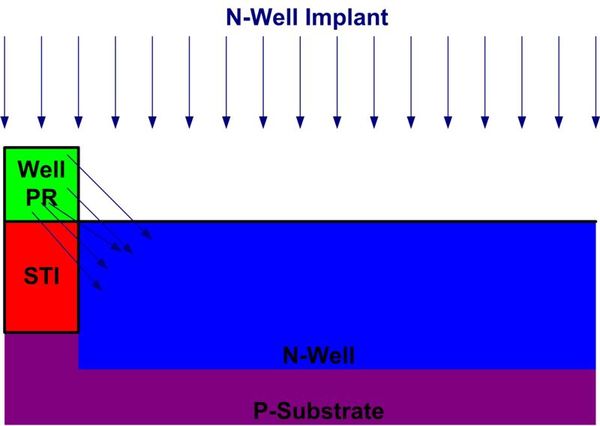

在先進半導體製程中,除了LOD (Length of Diffusion) Effect外,另ㄧ個常被提到的問題就是Well Proximity Effect,簡稱WPE,中文叫"井鄰近效應"。白話ㄧ點來說,是靠近井(Well)所造成的效應。

WPE的原因

- Sep 08 Mon 2008 00:52

-

Introduction to LOD Effect (下)

在Introduction to LOD Effect (上)一文中,已經簡單的介紹LOD (Length of Diffusion) Effect,接著來談談如何降低LOD Effect對電路的影響。LOD Effect有兩個重要參數SA、SB,由前文得知我們可以預先估計SA、SB的長度代入模擬中,這樣就可以精確的把LOD Effect考慮進去。不過實際電路設計時,你無法很準確的估計每個Device的SA(SB),尤其是Analog Circuit Layout上,還需考慮許多對稱的問題。所以一般我們只預估重要設計(Critical Block)裡面的SA(SB),再利用Layout上的技巧來降低LOD Effect對電路的影響。(註一)

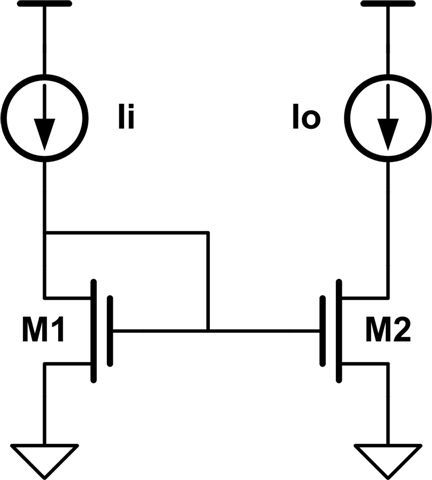

這裡用一個Current Mirror電路為例子,如圖一,Ii為輸入電流、Io為輸出電流。

圖一:

假設我們要設計Ii=Io,也就是要MOS1=MOS2。我們可以單獨把MOS1和MOS2畫出來,且SA1=SA2、SB1=SB2,如圖二。這樣LOD Effect對MOS1和MOS2的影響是相同的。

圖二:

圖二是MOS1和MOS2各只有一個Finger的狀況,假如是MOS1和MOS2為Multi Fingers呢?圖三為MOS1和MOS2各有2個Fingers的狀況,雖然MOS1和MOS2裡各自兩個Finger的SA、SB不同,但對MOS1、MOS2來說只要SA11=SA21、SB11=SB21、SA12=SA22且SB12=SB22,MOS1就是等於MOS2。所以當我們要設計Ii=Io(MOS1=MOS2)時,不論是否為Single Finger或是Multi Fingers,我們只要確定MOS1和MOS2的Layout一模一樣即可避免LOD Effect所造成的Mismatch,即使MOS1和MOS2畫在同一塊Diffussion上也是如此。

圖三:

如圖一,如果我們的設計不是Ii=Io,例如Ii=4*Io,這時我們可以單獨先把MOS1畫出來再把同樣的Layout複製4次成MOS2即可。不過為了要節省面積的關係,我們通常會把MOS1和MOS2畫在同一塊OD(difussion)上,這時Layout上就要特別注意。假設當SA(SB)大於5um時LOD Effect的影響小到可以忽略(註二), 圖四把MOS1和MOS2畫在同一塊OD上,所以我們必須把最外側(最左、最右)Fingers的OD延伸到大於5um的狀況下,這時將可以把LOD Effect影響忽略。

圖四:(MOS1有兩個fingers,MOS2有8個fingers。)

由圖四的例子可知,我們必須把重要電路(Ex: Current Mirror、Differential pair)的SA(SB)設計成>5um的狀況下,而其他不重要電路則可不遵守這樣的規則。如圖五,我們把Critical Cicuits擺在整個Diffussion中間,Non-Critical Cicuits(Ex: Switches、Dummy Devices)擺在兩旁,而Critical Cicuits最外側(最左、最右)Fingers其Gate到OD距離必須大於5um。

圖五:(Critical Circuits有6個fingers,Non-Critical Circuits有4個fingers。)

所以利用Layout上的技巧來降低LOD Effect對電路的影響最大原則就是"重要電路(Ex: Current Mirror、Differential Pair)的SA(SB)設計成>5um"(註二),其它的layout對稱問題就如一般的類比電路佈局技巧一樣(註三)。

註一:如果能預估所有元件的SA(SB)是再好不過了。

註二:不同製程下,可容忍的gate到diffusion長度皆不同,在設計電路時,要先找到這個值,在這裡是假設5um。

註三:類比電路佈局技巧可參考台北大學黃弘一教授的"混合信號積體電路設計與佈局"講義。

延伸閱讀1:Introduction to LOD Effect (上) by BuBuChen

參考文獻(References):

[1] Y. M. Sheu, et al., "Impact of STI Mechanical Stress in Highly Scaled MOSFETs," in Proc. IEEE International Symposium on VLSI Technology, Systems and Applications, 2003, pp. 76-79.

[2] P. G. Drennan, et al., "Implications of Proximity Effects for Analog Design," in Proc. IEEE Custom Integrated Circuits Conference, 2006, pp. 169-176.

- May 07 Wed 2008 00:52

-

Introduction to LOD Effect (上)

在先進的CMOS製程裡,LOD (Length of Diffusion) Effect將會是影響類比電路的一個重要參數。

剛好最近讀了一些有關LOD Effect的文章,發現LOD Effect的資訊幾乎都是英文的,故想用正體中文把這LOD Effect做個簡單的介紹,讓初次碰到LOD Effect的Designer可以快速進入狀況。

我把文章分成上、下兩篇,上集先簡單介紹LOD Effect,接著是如何模擬LOD Effect對MOS的影響。

而下集介紹如何避免LOD Effect對電路的影響。

什麼是LOD Effect?

LOD是Length of Diffusion 的縮寫,直接翻譯就是擴散區長度所造成的影響。從025um以下的製程,元件與元件間是利用較先進的STI(Shallow Trench Isolation)的方法來做隔絕。由於STI的作法,會在substrate上挖出一個溝槽,再填入二氧化矽當絕緣層。這個在substrate挖出溝槽的動作會產生應力的問題,由於FOX(Field Oxide)到Poly Gate的距離不同,應力對MOS的影響也不同。所以當擁有相同的Gate Length和Gate Width的兩個MOS,因為擴散區長度不同造成其電流不同。

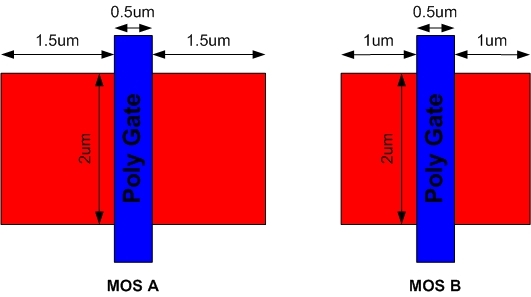

如下圖一,兩個MOS (A和B)其Gate Length與Gate Width皆為0.5um和2um,但由於擴散區分別為1um和1.5um,所以其電流大小並不同。

圖一:

- Nov 02 Fri 2007 23:04

-

Level Shifter

出包了~~~我的第一個project原本以為會順順利利完成~~~

結果還是出包了~~~~很幹~~~ 心情不好~~~~

我做的design沒出問題,反而是客戶拿別人的IP來用出包了~~~

沒幫他們check出來問題...................

問題出在IP裡的level shifter上,

結果還是出包了~~~~很幹~~~ 心情不好~~~~

我做的design沒出問題,反而是客戶拿別人的IP來用出包了~~~

沒幫他們check出來問題...................

問題出在IP裡的level shifter上,

- May 23 Wed 2007 22:15

-

如何在HSPICE中產生眼圖(Eye Diagram)

最近正在做PLL/DLL的設計,需要把輸出訊號用眼圖的方式表現來評估抖動(jitter)。

以下就是介紹產生眼圖的方法。

首先把下列紅色文字部分貼到你的netlist裡去,並做些許的修改。

.param period='10n $set eye diagram periodiod

.param t_start='0.1m' $set eye diagram start time

.probe tran eyetime=

+par('.5*(sgn(TIME-t_start)+abs(sgn(TIME-t_start)))*(TIME-t_start-period*int((TIME-t_start)/period))')

以下就是介紹產生眼圖的方法。

首先把下列紅色文字部分貼到你的netlist裡去,並做些許的修改。

.param period='10n $set eye diagram periodiod

.param t_start='0.1m' $set eye diagram start time

.probe tran eyetime=

+par('.5*(sgn(TIME-t_start)+abs(sgn(TIME-t_start)))*(TIME-t_start-period*int((TIME-t_start)/period))')

- May 23 Wed 2007 21:55

-

How to generate eye diagram in HSPICE

Because I am doing PLL/DLL design, I need to generate eye diagram in HSPICE.

Please paste the following sentences (red words) in your netlist and then run simulation.

.param period='10n $set eye diagram periodiod

.param t_start='0.1m' $set eye diagram start time

.probe tran eyetime=

+par('.5*(sgn(TIME-t_start)+abs(sgn(TIME-t_start)))*(TIME-t_start-period*int((TIME-t_start)/period))')

Please paste the following sentences (red words) in your netlist and then run simulation.

.param period='10n $set eye diagram periodiod

.param t_start='0.1m' $set eye diagram start time

.probe tran eyetime=

+par('.5*(sgn(TIME-t_start)+abs(sgn(TIME-t_start)))*(TIME-t_start-period*int((TIME-t_start)/period))')

- Aug 08 Mon 2005 21:39

-

32k oscillator

- Jun 13 Mon 2005 21:39

-

counter的架構

經雷克斯的提醒

這樣去count出來的結果本來就會算錯(不穩定)~

即使我RC oscillator再準也是如此

應該要好好計算一下

到底是我這的問題,還是跟本是digital那的架構問題

這樣去count出來的結果本來就會算錯(不穩定)~

即使我RC oscillator再準也是如此

應該要好好計算一下

到底是我這的問題,還是跟本是digital那的架構問題