談完LOD Effect,就不得不再談談WPE。

在先進半導體製程中,除了LOD (Length of Diffusion) Effect外,另ㄧ個常被提到的問題就是Well Proximity Effect,簡稱WPE,中文叫"井鄰近效應"。白話ㄧ點來說,是靠近井(Well)所造成的效應。

WPE的原因

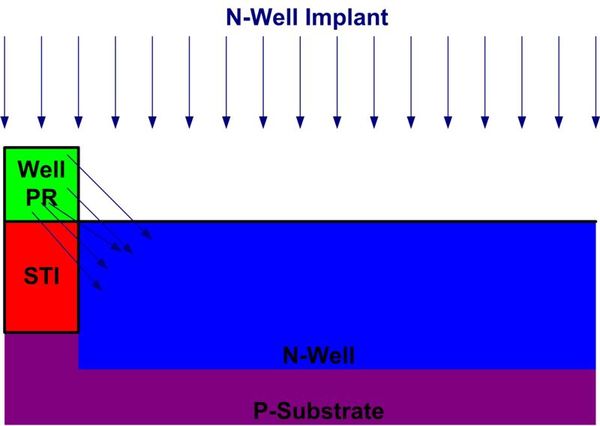

圖一是N-Well的製作過程,Well PR是指Well Photo Resistant,是用來阻擋Well Implant,也就是不是形成N-Well的地方就有Well PR,來把N-Well Implant阻擋掉。可是Well PR擋掉的部份會跑到Well去,造成在靠近Well邊緣的位置參雜濃度比較高,也就是整個Well的參雜濃度就會不均勻,造成靠近Well邊緣的Device其Vt(Threshold Voltage)比一般的Device高。所以我們在電路設計和Layout上必須要考慮WPE的影響。

圖一:

如何模擬WPE?

BSIM4.5之後的model才開始支援WPE的模擬,目前晶圓廠的先進製程(90nm、65nm)都已提供支援BSIM4.5的Model給客戶使用了。

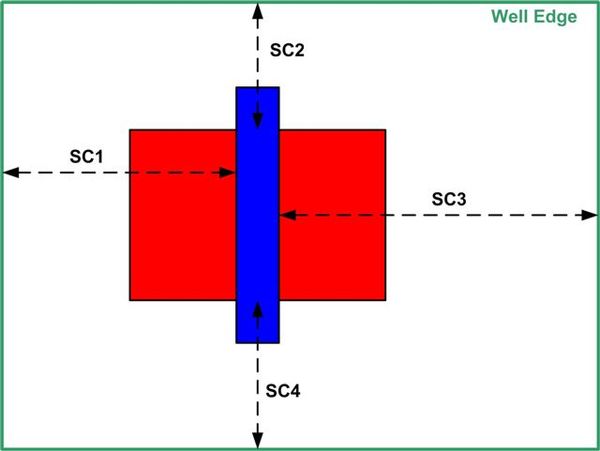

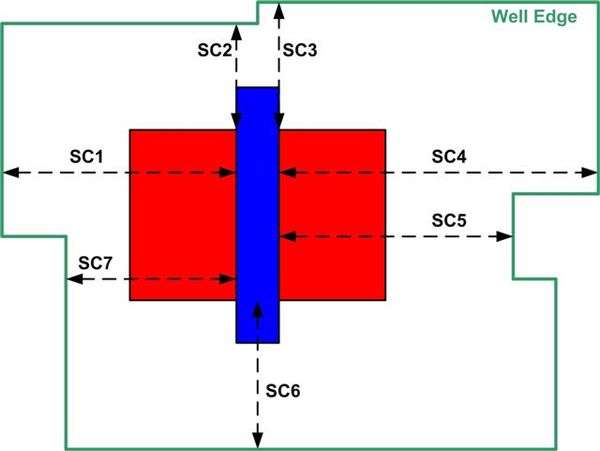

由前ㄧ段的介紹可知,Device到Well Edge的距離是WPE最重要也是唯一的設計參數(SC)。由於Device到周圍的Well Edge皆不同,所以會有許多不同的的SC值。如圖二(Well為方形)裡的Device,就有四個SC值(SC1、SC2、SC3和SC4);如果Well Edge為不規則形狀,就會有更多不同SC值,如圖三。

圖二:

圖三:

由於ㄧ個Device有許多不同的SC值,且每個SC值所佔的比例也不同,所以真正在計算WPE參數時將會非常複雜(註一)。在做pre-sim時候,我們就只把Device裡最小的SC代入Netlist中。假設圖二裡的Device,其SC1=3um、SC2=2um、SC3=4um、SC4=2um,所以Netlist描述如下面M1。

======================================================

M1 VD VG VS VB NMOS L=0.5U W=2U SC=2u

======================================================

當Layout完成後,寄生參數萃取軟體(Layout Parasitics Extraction )會把這些不同的SC值作計算,最後會得到另三個參數SCA、SCB、SCC,所以post-sim的netlist裡對Device的描述將會如下面M2ㄧ般。

======================================================

M2 VD VG VS VB NMOS L=0.5U W=2U SCA=2.25 SCB=2.08e-4 SCC=4.56e-8

======================================================

如何降低WPE的影響?

前面提到當Device離Well Edge越遠時,WPE的影響就越小。假如當所有的SC皆大於3um時,WPE的影響可以忽略,那我們Layout可畫成如下圖四的狀況,這樣就可以把WPE的影響降低。ㄧ般的晶圓廠所提供的Design Rule會告訴Designer這方面的資訊,我們只要照著個Rule去畫即可。

圖四:

最後來談談個人的經驗,當你有考慮LOD Effect時候,一般也已經考慮到WPE。因考慮LOD Effect時候,兩旁會加上Dumm,再加上Analog Circuit周圍會包上Guard Ring,所以Device到Well Edge的距離都已經接近甚至超過Design Rule裡的要求了。

註一: 做pre-sim時,是代入SC這個參數;做post-sim時,則是代入SCA、SCB、SCC這三個參數。SCA、SCB、SCC是由Device的每個SC計算而來,Designer並無法由Layout上直觀的得到這三個參數,必須透過寄生參數萃取軟體(Layout Parasitics Extraction )幫忙。有關SCA、SCB、SCC參數可參考BSIM4.5的文件。

延伸閱讀1:Introduction to LOD Effect (上) by BuBuChen

延伸閱讀2:Introduction to LOD Effect (下) by BuBuChen

參考文獻(References):

[1] P. G. Drennan, et al., "Implications of Proximity Effects for Analog Design," in Proc. IEEE Custom Integrated Circuits Conference, 2006, pp. 169-176.